# FPGA を用いた相関計測装置の開発

電気通信大学 情報理工学部 先進理工学科

森永研究室 1313175 般若大和

指導教員 森永 実 助教

## 1 序論

近年、情報技術の発達により、世界の通信量は爆発的に増加している。現在使用されている RSA 暗号等の公開鍵暗号方式はその堅牢性を素因数分解にかかる時間を担保としているため、量子コンピュータ等の技術の進歩によりやがて突破されることが懸念されている。そこで、量子暗号通信が注目されている。これは、量子状態が観測により変化することを利用することで、他者による通信の傍聴を記録することが可能であることを利用した、通信経路の安全性を担保する暗号情報技術である。これには、単一光子の生成、及び測定する技術が必要である。本研究では、FPGA(Field-Programmable Gate Array) を用いて単一光子を測定する機器を製作し評価する。

### 1.1 研究の目的

本研究の目的は、FPGA ボードを用いて、光検出器が検出した 2 個の光子の時間間隔を PC に送る、相関計測装置の開発である。FPGA を用いることで、ハードウェア回路による高速処理が安価に構成することが可能である。

## 2 相関計測装置による単一光子の測定原理

### 2.1 単一光子状態

[单一光子] とは、理論的には一つの時空間モードに対して一つの時空間モードに対して光子が 1 個励起されている状態を指すが、実験的には、ある時空間において光子を検出した際に 2 個以上の光子が検出される確率が 0 である状態を指す場合が多い [1]。後者の場合には、光子数は 0 または 1 であって、前者（光子数が 1 に確定した状態）とは異なるが、2 個以上の光子が存在しないことが確定できることから、量子暗号における秘匿性の保持等において実用上重要な状態である。

单一光子状態を論じるうえで重要な光子の時間的な單一性は、2 次の自己相関関数（強度相関関数）

$$g^{(2)}(\tau) = \frac{\langle \hat{a}^\dagger(t)\hat{a}^\dagger(t+\tau)\hat{a}(t+\tau)\hat{a}(t) \rangle}{\langle \hat{a}^\dagger(t)\hat{a}(t) \rangle^2} \quad (1)$$

で定量的に表すことができる。ここで、 $\hat{a}^\dagger(t)$  および  $\hat{a}(t)$  はそれぞれ時刻  $t$  における光子の生成、消滅演算子、 $\tau$  は光子の時間間隔である。单一光子状態では、同時に 2 個以上の光子が観測されないため、 $g^{(2)}(0) = 0$  である。光を古典的な電磁波として扱うと、 $g^{(2)}(0) \geq g^{(2)}(\tau)$  となるため、これは光を粒

子として扱った量子力学的現象である。

### 2.2 光子相関の実験

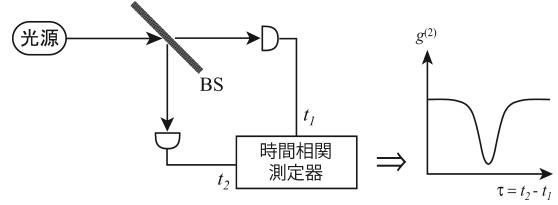

強度相関関数は Hanbury Brown および Twiss の方法 [2] によって実験的に評価する。図 1 に光子検出器を用いた光強度の時間相関測定系の例を示す。光源からの光を 50%:50%

図 1 光子検出器を用いた光強度の時間相関測定の概念図 [1]

ビームスプリッタに入射し、光束を 2 つに分割した後、2 個の光検出器で受光する。それぞれの光検出器の出力パルスの時間差  $t_2 - t_1 = \tau$  を測定し、その分布から強度相関関数が求められる。光源が単一光子でない場合、入射した光はビームスプリッタで分割され、2 つの光検出器で同時に検出される。光源が単一光子の場合、それぞれの光検出器に同時に光が受光されることはないため、ヒストグラムにおける  $\tau = 0$  での分布にディップが発生する。これにより、光源が単一光子であることが証明される。

## 3 相関計測装置の製作

本研究では、2 つの光検出器からの信号を FPGA を用いて読み取り、その時間差を PC(パソコンコンピュータ) に送信し、PC 上で集積したデータを処理するシステムを構築する。

### 3.1 FPGA

FPGA とは、使用者が自由に論理回路を設定できる IC(集積回路) である。MPU(MicroProcessing Unit) は、コンピュータプログラミング言語により記述されたソフトウェア演算を逐次実行するが、FPGA はハードウェア記述言語等によって構成された論理回路により複数の演算を並列処理する。したがって、汎用 MCU に比べて、FPGA は同時に複数の入力に対して並列に処理することが得意である。また、本研究では、ナノ秒レベルの時間間隔の電気信号を扱う。演算の処理速度はクロック周波数に依存する。これには、GHz レベルのクロック周波数が必要であるが、一般的な組み込み MCU(Micro Control Unit) では 100MHz 程度までしか扱えないため、FPGA を用いたハードウェアによる高速処理が適している。

### 3.2 実装

#### 3.2.1 FPGA ボード

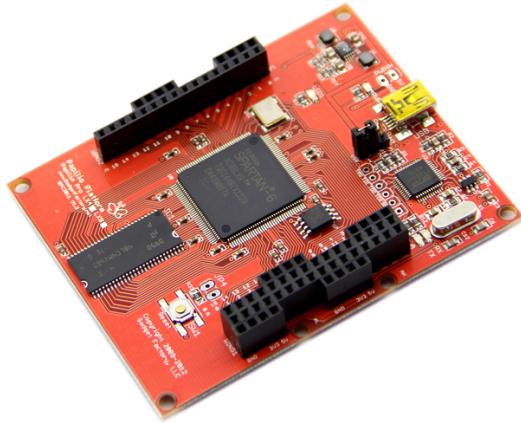

使用したFPGA ボードについて記す。Gadget Factory 社が行っているオープンソース FPGA プロジェクト Papilio より、開発用ボード Papilio Pro(図 3)を使用した。主要諸元は以下となる[3]。

- Spartan 6 LX9 FPGA (Datasheet[4])

- High efficiency LTC3419 Step Down Dual Voltage Regulator (Datasheet[5])

- Dual Channel FTDI FT2232 USB 2.0 Full Speed Interface (Datasheet[6])

- 64Mbit Micron MT48LC4M16 SDRAM (Datasheet[7])

- 64Mbit Macronix MX25L6445 SPI Flash (Datasheet[8])

- 48 I/O pins arranged in a Papilio Wing form factor

- 32Mhz Crystal Oscillator

図 2 Papilio Pro Board[3]

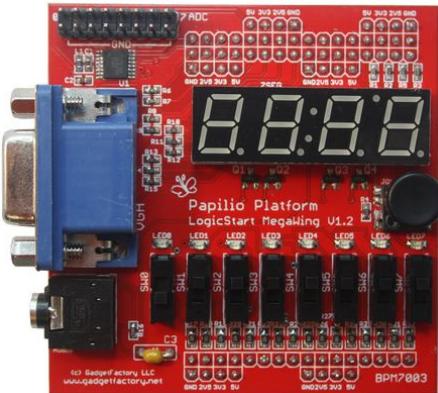

FPGA 開発環境には Xilinx 社提供の ISE を使用し, Verilog-HDL にて記述した。また,Papilio Pro に装着可能なアタッチメントである LogicStart MegaWing[9] を用いて製作を行った。これは、入出力ポートの一部を 7 セグメント LED やスライドスイッチ等に接続し,FPGA の動作の確認に用いた。

図 3 Papilio LogicStartMegaWing [9]

#### 3.2.2 構成

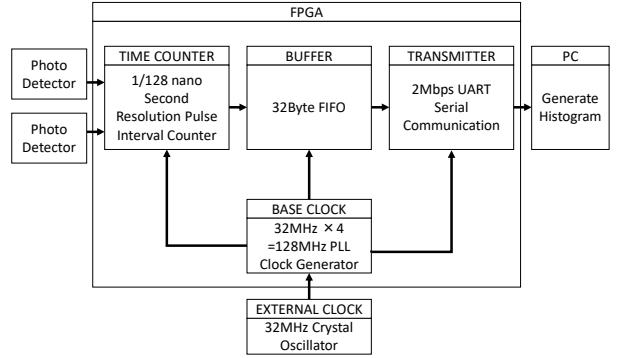

図 4 に、製作した相関測定装置のブロック図を示す。外部

図 4 ブロック図

クロックの 32MHz 水晶振動子を FPGA 内臓の PLL(Phase-Lock Loop)回路を用いて 128MHz に倍増し、メインクロックとした。これにより、測定分解能が 31.25 ナノ秒 (=1/32MHz) から 7.8125 ナノ秒 (=1/128MHz) に上がり、目標とする 10 ナノ秒の時間間隔の測定が可能となる他、PC への出力に扱う UART 通信のボーレートを FT2232D の通信速度の上限である 2Mbps で安定動作させることができた。2 つの光検出器によって電気信号に変換された光パルスを FPGA で受け取り、どちらか片方からの入力からタイマカウントを開始し、もう一方からの入力までの時間差を計測する。このときの時間分解能は動作クロックに依存するため、1bitあたりは約 (1/128MHz)=7.81 ナノ秒となる。これを、符号付き 8bit 整数として FIFO バッファー回路を経由して UART 通信回路にて PC に送信する。PC では python スクリプトで記述したプログラムを用いて受け取ったデータを CSV およびヒストグラム画像として保存する。

製作した相関測定装置の諸元は以下となる。

|         |             |

|---------|-------------|

| 動作周波数   | 128MHz      |

| 時間分解能   | 7.81ns      |

| 測定時間幅   | -1000~992ns |

| 入力信号レベル | 3.3V(LVTTL) |

| 出力信号    | 8bit 符号付き整数 |

## 4 評価実験

製作した相関測定装置を評価する。

### 4.1 評価方法

光検出器からの信号を模擬した信号源としてファンクションジェネレータを用いて、外部からのパルスに対する動作を確認し、システムクロックと同期しない信号に対する動作を確認した。また、高速な入力に対する応答性能の確認のため、FPGA 内部でパルスを生成し、これを光検出器からの模擬信号源として FPGA の入力と接続し、その動作を確認した。

### 4.2 結果および考察

以下のヒストグラムの縦軸は頻度、横軸は時間差  $\tau$  を示す。

#### 4.2.1 外部入力に対する動作検証

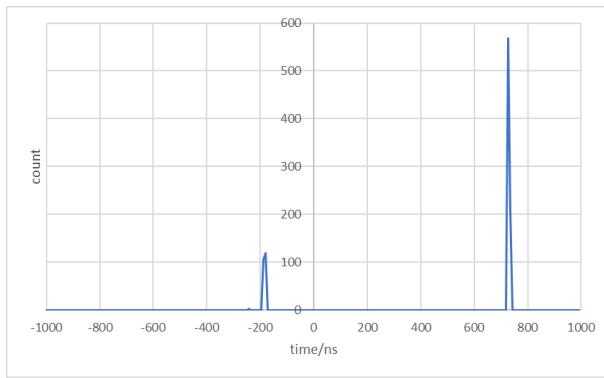

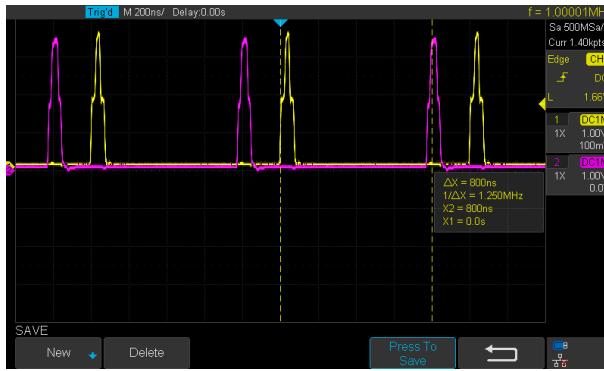

ファンクションジェネレータから  $f=1000\text{kHz}$  周期でパルスを時間差  $\tau$  で 2 つ出し、相関測定装置で時間差を測定した。図 5 は  $f = 1000\text{kHz}, \tau = 800\text{ns}$  として設定したときのヒストグラム、図 6 はその入力波形である。ヒストグラムのピークは-200ns および+730ns 付近に現れている。前者はパルスの周期が 1000ns であるため、パルス幅の測定に周期との差である 200ns が現出している事によるものである。後者はパルス幅が時間分解能 7.81ns に対して大きいため、パルスの終端部を測定開始時刻として処理していることによるものである。

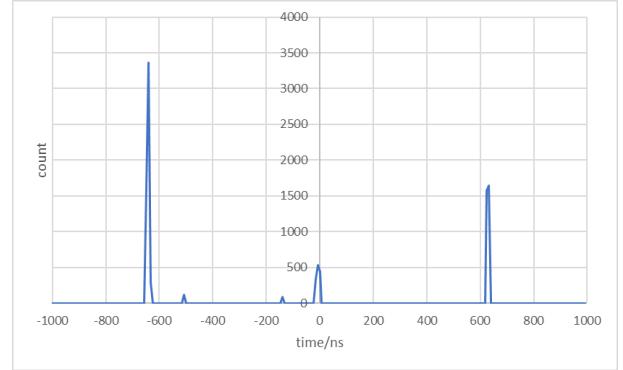

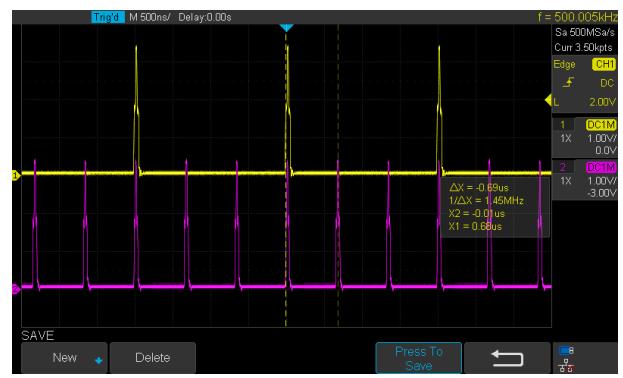

図 7 は  $f_1 = 1500\text{kHz}, f_2 = 500\text{kHz}$  として設定したときのヒストグラム、図 8 はその入力波形である。入力波形より、パルスの時間幅は-666,0,+666 で分布することが考えられるが、ヒストグラムにおいて同様の結果が取得できている。それぞれのピーク強度にはばらつきがあるが、これは  $f_1$  の入力パルス幅が  $f_2$  に比べて大きいため、測定開始終了処理に偏りができたことから生じたものである。

これらの結果より、動作クロックと同期していない外部からの入力に対して正常に動作していることがわかる。

図 5  $f = 1000\text{kHz}, \tau = 800\text{ns}$  のヒストグラム

図 6  $f = 1000\text{kHz}, \tau = 800\text{ns}$  の入力

#### 4.2.2 連続動作の検証

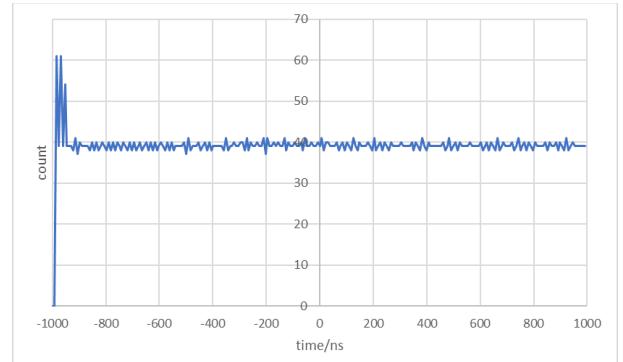

FPGA の内部クロックを用いて、 $f_1, f_2$  の 2 種類の周期のパルスを生成し、その出力を相関測定装置に接続し時間差を測定した。図 9 は  $-1000\text{ns} < \tau < 1000\text{ns}$  の範囲で一様に分布するように  $f_1, f_2$  を設定したときのヒストグラムである。桁上りの演算に不具合があり、 $\tau = -1000\text{ns}$  付近での相関に乱れが生じたが、実際の光パルスの時間幅の測定では影響の小さい領域である。したがって、時間間隔  $\tau$  の測定が正常に動作していることがわかる。

図 7  $f_1 = 1500\text{kHz}, f_2 = 500\text{kHz}$  のヒストグラム

図 8  $f_1 = 1500\text{kHz}, f_2 = 500\text{kHz}$  の入力

図 9  $f_1 = \frac{128}{255}\text{MHz}, f_2 = \frac{128}{254}\text{MHz}$  ヒストグラム

## 5 結論

### 5.1 まとめと今後の展望

4章より、今回製作した相関測定装置の一連の機能は十分に示された。桁上り処理の不具合は、実際の光パルスの時間差の測定に対して影響の小さい領域であるが、この改善も必要である。使用したFPGAの残りブロックRAMの容量に余裕があるため、他の機能の追加は可能である。

現在の試作では、7.81ナノ秒となっているが使用しているFPGAの機能に8bitデシリアライザがあるため、ここから更に8倍、すなわちナノ秒以下の分解能で測定することが可能である。それに伴い、出力信号のデータが8bitを超えるため、8bitUART通信で送信するときのデータフォーマットを再考する必要がある。また、実際の光検出を接続した測定はまだ行ってないため、実際に測定を行い、有効性を検証する必要がある。

## 参考文献

- [1] 圭一枝松. 単一光子・相関光子発生技術の進展. 光学, Vol. 37, No. 8, pp. 440–446, aug 2008.

- [2] R Hanbury Brown and Richard Q Twiss. Correlation between photons in two coherent beams of light. *Nature*, Vol. 177, No. 4497, pp. 27–29, 1956.

- [3] Gadget Factory. Papilio pro. <https://papilio.cc/index.php?n=Papilio.PapilioPro>.

- [4] Xilinx. Spartan-6 family overview. [https://www.xilinx.com/support/documentation/data\\_sheets/ds160.pdf](https://www.xilinx.com/support/documentation/data_sheets/ds160.pdf).

- [5] Linear Technology. Ltc3419 - dual monolithic 600ma synchronous step-down regulator. <https://www.analog.com/media/en/technical-documentation/data-sheets/3419fa.pdf>.

- [6] FTDI. Ft2232d dual usb to serial uart/fifo ic. [https://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS\\_FT2232D.pdf](https://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT2232D.pdf).

- [7] Micron. 64mb: x4, x8, x16 sdram. [https://www.micron.com/-/media/client/global/documents/products/data-sheet/dram/64mb\\_x4x8x16\\_sdram.pdf](https://www.micron.com/-/media/client/global/documents/products/data-sheet/dram/64mb_x4x8x16_sdram.pdf).

- [8] MXIC. Mx25l6445e high performance serial flash specification. <https://www.macronix.com/Lists/Datasheet/Attachments/7330/MX25L6445E,%203V,%2064Mb,%20v1.8.pdf>.

- [9] Gadget Factory. Logicstart megawing. <https://papilio.cc/index.php?n=Papilio.LogicStartMegaWing>.